开篇:行业震荡下的清醒认识

近日,芯片行业因EDA工具「断供」事件再次被推到了舆论的风口浪尖。作为深耕数字EDA前端工具的从业者,我们亲历了行业从技术封锁初期的焦虑,到如今全产业链协同破局的蜕变。本文不聚焦短期博弈,而是希望从技术视角,剖开国产EDA工具的真实发展脉络——那些被汗水浸润的代码、被反复推翻又重构的算法模型,以及一家本土科技企业在解决「卡脖子」困境中选择的「艰难而正确」的道路。

一、行业全景:在74%的阴影下突围

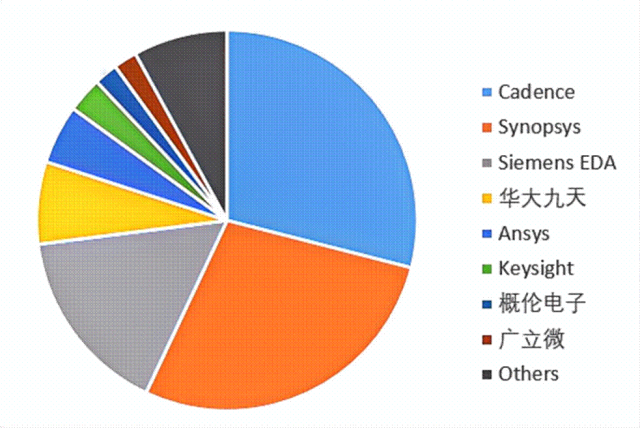

2024年全球EDA市场被三家欧美公司牢牢控制,其中Synopsys占比32%、Cadence占比29%、Siemens EDA占比13%,其中数字EDA产品领域占比更高。图2为2024年EDA行业市场格局图。

图2 EDA行业市场格局

1、被垄断的「芯片之母」

EDA(电子设计自动化)贯穿芯片设计、验证、制造的全流程,其重要性堪比建筑行业的「图纸+工具包」。全球市场中,Synopsys、Cadence和Siemens EDA形成铁三角,2024年在中国市场中,合计占据约74%的市场份额。对于芯片工程师而言,这意味着:

(1)数字设计需依赖其仿真器、综合工具、布局布线工具等;

(2)制造环节需适配其工艺库、物理验证工具等;

(3)先进制程研发更被其全流程工具链深度绑定。

国产EDA行业虽已诞生华大九天、概伦电子等上市公司,但整体仍处于「填空」阶段。比如在模拟芯片领域,华大九天已实现全流程工具覆盖,但在数字芯片领域——这个占据EDA市场60%以上份额的核心战场,仍是国产EDA工具需攻克的「娄山关」。

2、数字EDA工具的复杂性

数字EDA工具的复杂性远超想象:

(1)技术深度:仅仿真器就涉及编译器、调度算法、事件驱动机制等底层技术,Synopsys的VCS产品历经30年迭代才成行业标杆。

(2)生态广度:需兼容SystemVerilog等硬件语言,需适配台积电/中芯国际等多厂工艺库,任何环节脱节都可能导致设计流中断。

(3)验证难度:一颗7nm芯片的验证可能需要跑通百万种场景,工具稳定性不足可能会直接导致流片失败。

这种复杂性,使得国产数字EDA工具的突破不能只靠「单点突击」,而需构建从底层组件到全流程工具的完整生态链。

二、破局之道:从「拿来主义」到「根技术重构」

1、逆向工程的陷阱与正向研发的决心

入行时,我们曾面临两种选择:

捷径:购买国外组件授权,快速拼装出「能用」的工具。

险路:从零开始,开发底层模块,构建完全自主的技术底座。

我们最终选择后者,源于一个朴素的认知:没有编译器和求解器等底层组件,就如同建筑师建造房子没有水泥的配方,将永远受制于人。

2023年之前,技术团队隐于实验室,完成了三件事:

(1)自研编译器:支持SystemVerilog全语法解析,并应用到了仿真工具中。

(2)重构事件驱动引擎:自主设计调度算法,内存管理效率不断提升。

(3)建立测试基准:用大量芯片项目验证底层组件及模块,不断修复bug。

这段「不见产出」的时光,为后续的突破埋下伏笔。2022年底,首款仿真工具USIM1.0诞生,尽管性能仅为VCS工具的十几万分之一,却标志着「根技术」的突破和自主可控。

2、性能跃迁的「算法密码」

从2022年三季度开始,公司逐步将仿真工具的研发从功能实现转为性能优化,到目前为止已完成超6万倍的性能提升。图3为「九霄智能」仿真工具性能提升曲线图。

图3 「九霄智能」仿真工具性能提升曲线

从「能用」到「好用」,我们需走三条技术路径:

(1)并行计算优化:将单核仿真架构升级为并行架构,支持1024核协同运算。

(2)智能编译加速:引入AI预测模型,提前识别热点代码并优化执行路径。

(3)增量验证技术:仅重新运行变更部分的代码,减少90%的重复运算量。

2025年实测数据显示,新版USIM4.0在某芯片验证项目中,速度已达VCS的53%。更关键的是:这种提升不依赖算力堆砌,而是单纯依靠算法的优化和创新。

三、生态革命:开放授权背后的行业理想

随着产品的逐步成熟和推向市场,越来越多的生态问题摆在眼前。芯片设计需要的工具繁多,芯片公司虽然可从「九霄智能」获得部分商用产品,但要完成整个EDA工具包的国产化,还需要更多国产EDA公司的加入。为加速EDA国产化进程,避免本就短缺的研发力量投入到「重复造轮子」的工作中,「九霄智能」将逐步公开核心组件,从工具供应商逐步转变为生态共建者。

图4 「九霄智能」产品及底层组件架构

「九霄智能」的EDA产品采用统一的IDE界面,所有产品都在IDE界面下以独立的功能模块实施调用。图4为「九霄智能」产品及底层组件架构图,图4下方的编译器、求解器等基础组件,倾注了「九霄智能」大量的心血,已在大量产品中完成迭代和验证。即日起,「九霄智能」将开放产品和功能组件,欢迎芯片企业、高校和同行的深入合作。

1、五年免费计划:工具普惠的「破冰行动」

2025年6月起,我们将推出两项行业举措:

(1)核心工具免费五年:向所有芯片企业、科研机构开放仿真工具USIM3.0稳定版,支持UVM验证方法学,可直接接入现有设计流程。

(2)高校永久免费:为高校教学及学术研究提供无限期授权,欢迎更多高校,共建联合实验室。

2、底层模块开源:让行业不再「重复造轮子」

2025年7月起,我们将逐步开放底层模块的授权。这意味着:

EDA从业者无需从零开发基础组件,可直接基于「九霄智能」的技术,迭代上层工具。

芯片企业能定制化改造工具链,例如为车规芯片增加功能安全验证模块等。

科研团队可基于组件获得更多精准信息,例如通过Parser,更精准地协助大模型优化自动编写代码的流程。

此举源于一个共识:EDA行业的竞争,本质是生态体系的竞争。当国际巨头通过并购构建「工具-IP-工艺」的闭环时,国产阵营唯有打破「小而散」的格局,才能形成合力。

四、未来图景:在「卡脖子」中培育「反脆弱」

2023年,当仿真工具USIM1.0的性能仅为国际巨头产品的万分之一时,曾有客户笑称「这是用算盘在挑战计算器」。如今回头再看,那些在深夜逐行调试的代码、被推翻27次的算法模型……,正在编织国产EDA工具的「反脆弱」系统。

我们深知,EDA工具的国产化不是某一家企业的战斗。当华大九天在模拟领域构筑优势、概伦电子深耕制造环节时,「九霄智能」愿做数字前端的「铺路石」——开放核心技术,共享研发成果,让行业的每一份努力都能在自主生态中形成共振。

结语:

EDA工具的自主化道路,是用代码对抗封锁的无声战役,是用开放破解垄断的创新实验。当我们把编译器的代码从10万行级别推向百万行级别,把仿真工具的速度从万分之一提升至超越50%,我们始终相信:技术的价值不在于竞争,而在于让「中国芯」的每一次设计迭代,都不再受制于他人的工具链。

这是一个需要「慢功夫」的行业,而我们,愿意做时间的朋友!